文章插图

SPYGLASS截图,图片源自网络

(4)功能验证

这一步是验证芯片设计与预定的设计需求是否相符的关键步骤,主要是验证电路设计逻辑功能的正确性,而非电路的物理特性(后面的步骤会讲到物理验证) 。数字仿真器是数字集成电路逻辑功能验证的主要手段 。

随着超大规模集成电路的高速发展,高性能数字仿真器已经成为数字集成电路设计与验证中必备的一环 。近年来数字仿真器技术发展很快,当今主流数字仿真软件可以支持数十亿晶体管规模的超大规模集成电路的逻辑功能进行高效精确的仿真验证 。为了保证芯片的稳定性,这个阶段的过程时间会持续数月 。EDA工程师常用的EDA工具是Mentor(西门子EDA)的Modelsim、Synopsys的VCS和Candence 的NC-Verilog 。

【数字芯片是如何设计出来的呢?数字芯片设计的十大流程】

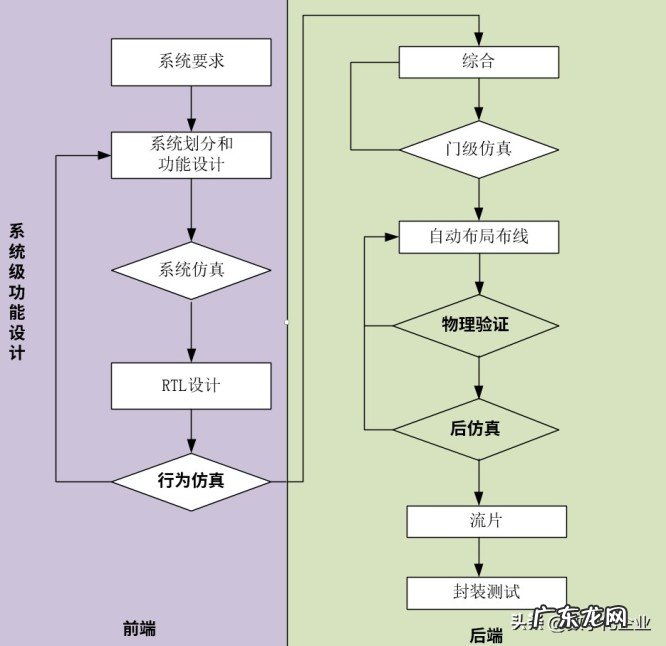

文章插图

功能仿真验证 在整个芯片设计流程中的位置(黑体)

后端设计

(5)逻辑综合(Synthesis)

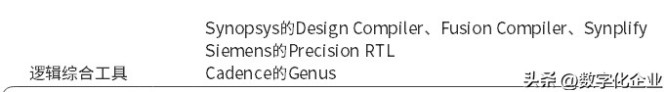

从这一步开始,就进入芯片设计的后端设计(物理设计)阶段了 。主要负责将RTL code转换为实际后端使用的Netlist(网表,包含了RTL中所有的逻辑信息,以及离散傅立叶变换、门控时钟和I/O等) 。网表的质量对芯片的布局布线工作起到决定性作用 。该过程需要考虑工艺的电特性和物理特性等因素,要尽可能做到Performance(性能)、Power(功耗)和Area(面积)的PPA优化 。Synthesis的质量在一定程度上取决于综合软件的性能,业界流行的两个逻辑综合工具是Synopsys的Design Compiler和Cadence的Genus,综合工程师的一个基本要求便是熟练的掌握两个工具的使用方法 。

文章插图

国内外布局布线工具厂商

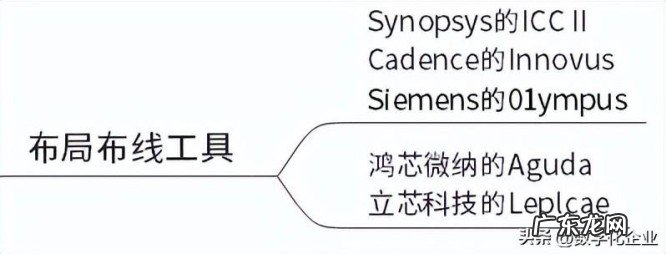

(6)布局布线(PD)

布局布线是数字后端中占比最大的工作,主要就是把网表转化成GDSII流格式(这是一种用于集成电路版图的数据转换的标准数据文件库格式,其中含有集成电路版图中的平面的几何形状、文本或标签等有关信息,由层次结构组成),确定各种功能电路的摆放位置 。PD的步骤包括Floorplan(布局规划)、Place(功能电路的摆放)、CTS(时钟综合)、Optimize(优化)、Route(布线)和ECO(工程变更)等,确保各个模块满足时序和物理制造的要求 。这个步骤是后端设计中最核心的工作 。布局布线对工具的依赖程度较强,而且工具操作相对来说较为复杂 。业界较为常用的是Cadence的Innovus和Synopsys的ICC 。

文章插图

国内外布局布线工具厂商

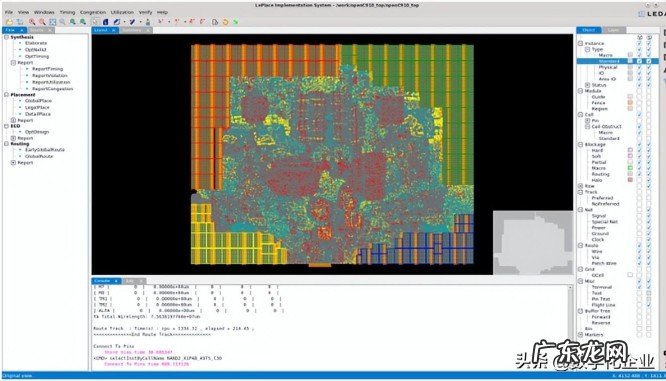

文章插图

Leplace图形界面

(7)静态时序分析(STA)

STA(Static Timing Analysis,静态时序分析)是芯片后端设计中的重要步骤 。芯片上有海量的极其微小的金属元器件,这些元器件的大小不一,通过引线流过这些元器件的延时会有不同,由于元器件过于微小,芯片的布局布线肯定会受到这些不同大小元器件和之间引线的各种限制,而静态时序分析则是模拟各种元器件间的互联和各种不同状况的仿真,找出存在的各种问题 。

静态分析需要保证芯片设计中所有的路径,满足内部时序单元对建立时间和保持时间的设计要求 。也就是说无论信号的起点是什么,信号都可以被及时地传递到该路径的终点 。同时,也要满足电平跳变时间、电容、噪声、等要求 。STA需要制定整个芯片的时序约束约束文件,选择芯片需要Signoff(签发)的Corner(工作范围)以及全芯片的Timing(时序) ECO流程,这个步骤的难度要求很高 。STA阶段应用较广的是Synopsys的Primetime和Cadence的Tempus软件 。值得一提的是国内鸿芯微纳的ChimeTime,它是一种静态时序签核工具,提供了SPICE仿真精度的签核结果 。

- 2023云南红河老旧小区改造计划是怎样的?改造内容有哪些?

- 业主为什么要交物业费?物业费定价原则是什么?

- 人心不足蛇吞象是什么意思?人心不足蛇吞象出处及历史典故

- 以小人之心度君子之腹是什么意思?历史典故及心理分析

- 知人知面不知心什么意思?知人知面不知心历史典故

- 失之毫厘谬以千里是什么意思?失之毫厘谬以千里历史典故

- 大红袍枸杞茶

- 冒充他人签合同是什么罪

- 最喜欢刁难他人的人面相是怎样

- 覆盆子怎么吃

特别声明:本站内容均来自网友提供或互联网,仅供参考,请勿用于商业和其他非法用途。如果侵犯了您的权益请与我们联系,我们将在24小时内删除。