CPU读取数据是怎样的顺序呢?在CPU需要数据的时候 , 遵循一级缓存〉二级缓存〉内存的顺序 , 从而尽量提高读取速度

文章插图

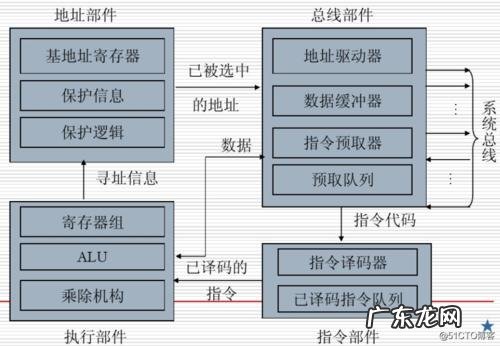

计算机如何保证cpu按程序规定的顺序执行指令呢?首先你要明白 , 程序有顺序执行的程序 , 也有并发执行的程序 。 对于顺序执行的程序 , 指令执行顺序是确切的(当然程序指令本身可能存在分支) , CPU只需要依序将指令装入指令寄存器 , 然后再执行即可 。 对于有多个处理器(或者多核)的系统 , 在执行并发程序时 , 指令执行的顺序是不确切的 。 即使是执行顺序程序 , 指令执行了顺序也可能不确定(聪明的CPU有可能将顺序程序的某些指令块优化成并行指令) 。

谁懂CPU读写数据的顺序过程 , 从哪里开始读 , 然后到哪里?CPU-一级指令缓存-二级数据缓存-前端总线-北桥-内存-硬盘(光驱或者U盘)给你说的 这个不好说的 你有病啊CPU内部将寄存器对接到数据总线上 , 使寄存器的每一位对接到一条数据线 , 等待接收数据 。

CPU将内存地址通过地址线发给内存 , 然后通过另外一条控制线发一个读请求 。

内存收到地址和读请求之后 , 将相应的存储单元对接到数据总线的另一端 , 这样 , 存储单元每一位的1或0状态通过一条数据线到达CPU寄存器中相应的位 , 就完成了数据传送 。

⑴顺序指令的执行情况 当CPU执行顺序指令时 , 程序计数器值的修改较为简单 。 若当前取得的指令是单字节指令 , 即将程序计数器的值加1;若当前取得的指令是双字节指令 , 即将程序计数器的值加2 , …;如果当前取得的指令是n字节 , 则将程序计数器的值加n 。

⑵分支转移指令的执行情况 在执行分支转移指令时 , 由分支转移指令的寻址方式确定下一条指令在主存中的地址 。 若分支转移指令的寻址方式是相对寻址 , 那么 , 程序计数器的值修改为当前地址加上相对偏移量;若分支转移指令的寻址方式是绝对寻址 , 即将转移指令中绝对转移地址送给程序计数器;当间接寻址方式的分支转移指令时 , 程序计数器的值从寄存器或主存中间接得到 。

文章插图

CPU的处理器的先后顺序 , 像奔腾赛扬什么的他们顺序?所有的90年代的奔腾1234然后赛扬了= =最新(好)的是酷睿I357

这是因特尔家的

其他的AMD啥啥我不太清楚= =赛扬是最低端 然后是奔腾 酷睿是最高级别的 酷睿也分I3 I5 I7 I7最高最贵 嘿嘿排列应该是酷睿-奔腾-赛扬-凌动

T4以下都是奔腾双核

【CPU顺序执行与乱序执行 cpu顺序】应为凌动处理器大多用于上网本 , 其划分不明朗 。 介于赛扬之间!简单的说 , 奔腾e系列都是65nm的 , 而酷睿的是45nm的 , 集成度更高 , 技术更先进 。 赛扬是intel的低端产品 , 有人这样比喻说赛扬是被阉过的cpu 。 赛扬系列的一级缓存和二级缓存都比较低 , 例如二级缓存都不超过512kbINTEL的CPU , 如果核心是同框架的话 , 依次从高到低排列是酷睿 奔腾 赛扬

特别声明:本站内容均来自网友提供或互联网,仅供参考,请勿用于商业和其他非法用途。如果侵犯了您的权益请与我们联系,我们将在24小时内删除。