- 收集许多Arm核心 。

- 增加现场可编程门阵列(FPGA) , 可编程逻辑 。

- 增加一种是自定义设计的网络处理器 。

管理侧网络后台任务是最先遇到资源消耗挑战问题的 , 在25bit/s下占用的CPU资源已经非常显著 。 智能网卡就是为卸载网络相关工作任务而设计的 。

DPU 数据处理:

从本质上来说 , 在智能网卡的基础上行 , 不仅仅是网络 , 而是整个I/O相关的工作任务处理都会面临资源消耗的挑战问题 , 因此DPU在网络卸载的基础上 , 加入了存储卸载及虚拟化卸载的解决方案 。

IPU 基础设施处理:

从云计算公司的角度来看 , 基础设施处理器平台不仅承载网络、存储及虚拟化的卸载 , 还需要承担安全、管理、监控等各种管理面的功能 , 更为关键的是物理隔离业务和管理:业务在CPU和GPU , 管理在DPU(或者更准确地称为IPU) 。 目前英特尔已经使用 FPGA 部署了 IPU , 微软、百度、京东云和 VMWare是买家 。 通过特定功能 , IPU可对数据中心中基于微服务架构的现代应用程序进行加速 。 谷歌和Facebook的研究表明 , 微服务通信开销可消耗22%到80%的CPU性能 。

// DPU目前的主要架构

▎基于FPGA的SmartNIC

Pro:灵活性高 , 可编程

可以像处理网络和存储一样处理计算 , 在开发上 , 可以如CPU一样具有高度的可编程性 , 也可以像在SoC解决方案上一样快速开发新功能 。 如赛灵思宣称 , 其Alveo U25与基于Arm多核的SmartNIC相比 , 在相同功率下 , 性能可提高10倍 。

▎基于ARM多核阵列

Pro:可以卸载明确定义的任务 , 例如标准化的安全和存储协议 , GPU可以从与DPU融合中受益

Con:

- 基于软件可编程处理器 , 由于缺乏处理器并行性 , 这些处理器在用于网络处理时速度较慢

- 多核 SmartNIC ASIC中的固定功能引擎无法扩展来处理新的加密或安全算法 , 因为它们缺乏足够的可编程性 , 只能适应轻微的算法更改 。

Pro:异构具有更高的灵活性 , 并能带来更高效的数据处理效率

Con:需要自研架构 , 研发投入较高 。 如国内中科驭数的KPU架构 , 他们将四类异构核组织起来 , 分别处理网络协议 , OLAP\OLTP处理 , 机器学习和安全加密运算核 。

目前的趋势是趋于折中 , 且专用核的比重越来越大 , 正在成为最新的产品趋势 , 以英伟达的BlueField2系列DPU来看 , 就包括4个Arm核及多个专用加速核区域 , Fungible的DPU则包含6大类的专用核 , 和52个MIPS小型通用核 。

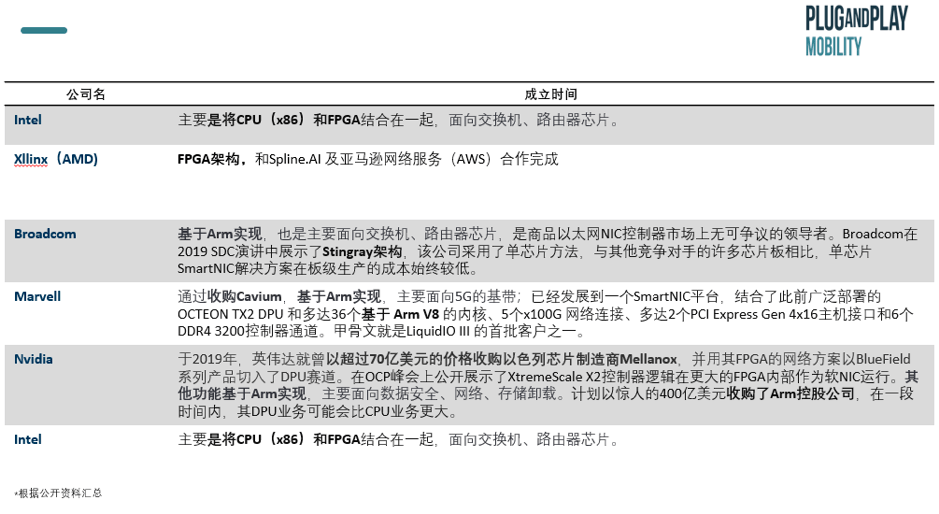

06 DPU赛道上主要玩家 // 大厂收购初创企业

【出行洞察:DPU市场火热,“芯”战场发展前景如何?】在DPU这一新兴芯片赛道上已有英伟达(收购Mellanox)、英特尔(收购Bearfoot )、Broadcom和Marvell(收购Cavium)、 Fungible(初创) 、Xllinx等巨头 , 主要以收购初创企业的方式完成 。

文章图片

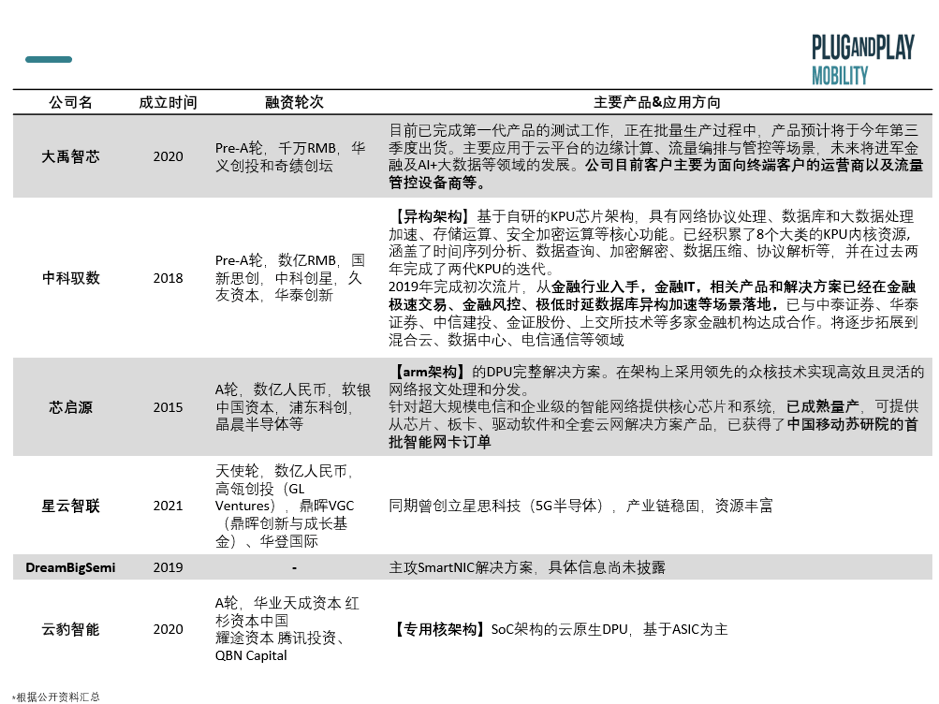

// 初创企业团队来自大厂背景 , 专注单一架构的芯片

他们成立时间大部分在2018年及以后 , 在半年内均完成了多轮融资 , 前期投资机构持续加码 。

文章图片

市场中DPU玩家与所有芯片厂商类似 , 在产业链中主要负责IC设计环节 , 仅有少部分设计框架设计 。

EDA:设计芯片的软件高度垄断:美国的Synopsys、美国的Cadence 和西门子旗下的 Mentor Graphicss占领95%市场 。

特别声明:本站内容均来自网友提供或互联网,仅供参考,请勿用于商业和其他非法用途。如果侵犯了您的权益请与我们联系,我们将在24小时内删除。