备注:若贴上SPI FLASH , 则最高元器件为SPI FLASH , 高度为2.2mm 。

底板设计注意事项5.1最小系统设计基于SOM-TL335x-S核心板进行底板设计时 , 请务必满足最小系统设计要求 , 具体如下 。

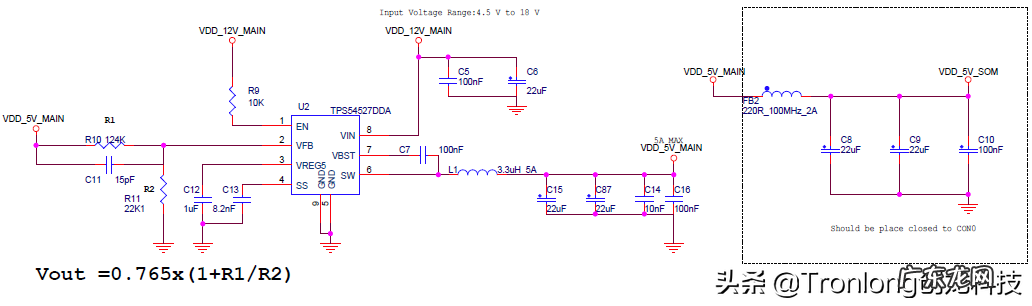

电源设计说明(1)VDD_5V_SOM

VDD_5V_SOM为核心板的主供电输入 , 电源功率建议参考评估板按最大5W进行设计 。

文章插图

图 15

VDD_5V_SOM在核心板内部未预留总电源输入的储能大电容 , 底板设计时请参照评估板原理图 , 在靠近邮票孔焊盘位置放置储能大电容 。

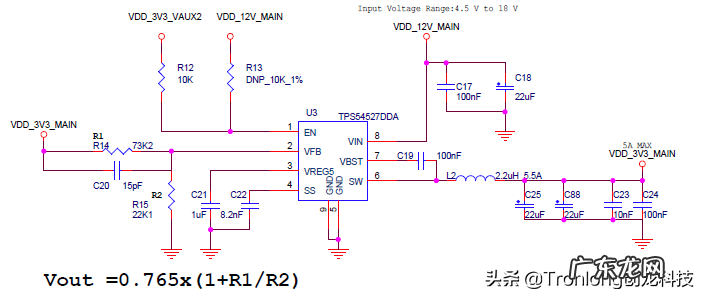

(2)VDD_3V3_MAIN

VDD_3V3_MAIN为底板提供的外设电源 。为使VDD_3V3_MAIN满足处理器的上电、掉电时序要求 , 推荐使用VDD_3V3_VAUX2电源来控制VDD_3V3_MAIN的电源使能 。

文章插图

图 16

(3)VDD_3V3_VAUX2

VDD_3V3_VAUX2为核心板输出的BOOT SET配置专用供电电源 , 最大电流为100mA , 请勿用于其他负载供电 。

文章插图

图 17

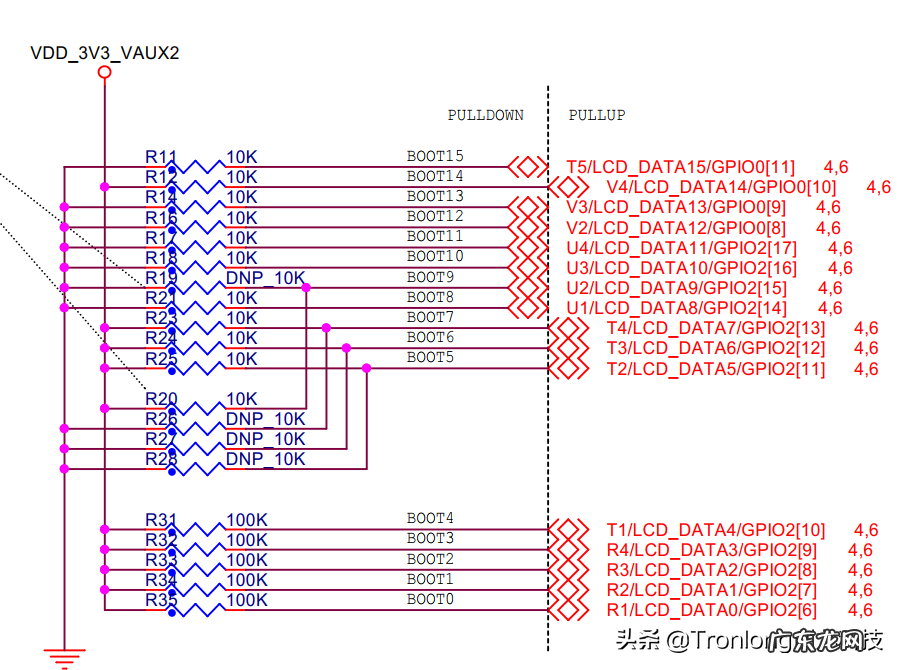

系统启动配置由于BOOT SET引脚与LCDC(LCD Controller)信号存在复用关系 , 若使用LCDC信号外接设备(例如接LCD显示屏) , 请保证AM335x在上电初始化过程中BOOT SET引脚电平不受外接设备的影响 , 否则将会导致AM335x无法正常启动 。

核心板内部BOOT[15:5]的已进行上下拉配置 , BOOT[4:0]均已设计100K上拉电阻 , 具体如下图所示 。设计系统启动配置电路时 , 请参考评估底板BOOT SET部分电路进行相关设计 。

文章插图

图 18

系统复位信号(1)SYS_RESETn

SYS_RESETn为AM335x的WARM RESET复位输出引脚 , 可用于控制外设的复位 。对于有严格上电复位顺序的外设 , 需要结合外设的上电和复位时序来使用SYS_RESETn 。

(2)RESETn_IN

RESETn_IN为AM335x的WARM RESET复位输入引脚 , RESETn_IN与SYS_RESETn通过100R电阻串接;核心板内部WARM RESET已设计10K上拉电阻 , 不使用RESETn_IN时请悬空处理 。(备注:WARM RESET可做输入和输出 。)

(3)PB_IN

PB_IN为PMIC的复位按钮输入引脚 , PB_IN在PMIC内部已上拉100K到5V , 默认情况可悬空处理 。

(4)nNMI

nNMI为非屏蔽中断引脚 , 核心板内部已设计上拉电阻 , 默认情况可悬空处理 。

5.2 功能引脚信号走线长度与阻抗说明如下为核心板MDIO、RGMII、USB、GPMC、LCDC(LCD Controller)等功能引脚信号PCB走线长度与阻抗说明 。

表 10

引脚信号名称

引脚功能

走线长度/mil

阻抗说明

R1

R1/LCD_DATA0/GPMC_A0/PR1_MII_MT0_CLK/EHRPWM2A/PRU1_R30[0]/PRU1_R31[0]/GPIO2[6]

LCDC

1677.68

单端50ohm

R2

R2/LCD_DATA1/GPMC_A1/PR1_MII0_TXEN/EHRPWM2B/PRU1_R30[1]/PRU1_R31[1]/GPIO2[7]

LCDC

1624.71

单端50ohm

R3

R3/LCD_DATA2/GPMC_A2/PR1_MII0_TXD3/EHRPWM2_TRIPZONE_INPUT/PRU1_R30[2]/PRU1_R31[2]/GPIO2[8]

LCDC

1491.31

单端50ohm

R4

R4/LCD_DATA3/GPMC_A3/PR1_MII0_TXD2/EHRPWM0_SYNCO/PRU1_R30[3]/PRU1_R31[3]/GPIO2[9]

LCDC

1547.88

单端50ohm

T1

T1/LCD_DATA4/GPMC_A4/PR1_MII0_TXD1/EQEP2A_IN/PRU1_R30[4]/PRU1_R31[4]/GPIO2[10]

LCDC

- 影之哀伤怎么做 影之哀伤任务在哪接

- 天气热的好句子 天气无敌热的句子

- 四年级运动会班级的口号

- 终极解码官方网站 终极解码淘宝客

- 跑步激励人心的口号 激励跑步的口号

- 精致的很有范的好听网名

- 超级奶爸俏老婆全文免费阅读 无敌小老婆作者

- 快滚加速器怎么使用

- 超级好的说说 超级无敌巨搞笑的说说

- 鲸鱼加速器永久免费版安卓 鲸鱼加速器

特别声明:本站内容均来自网友提供或互联网,仅供参考,请勿用于商业和其他非法用途。如果侵犯了您的权益请与我们联系,我们将在24小时内删除。